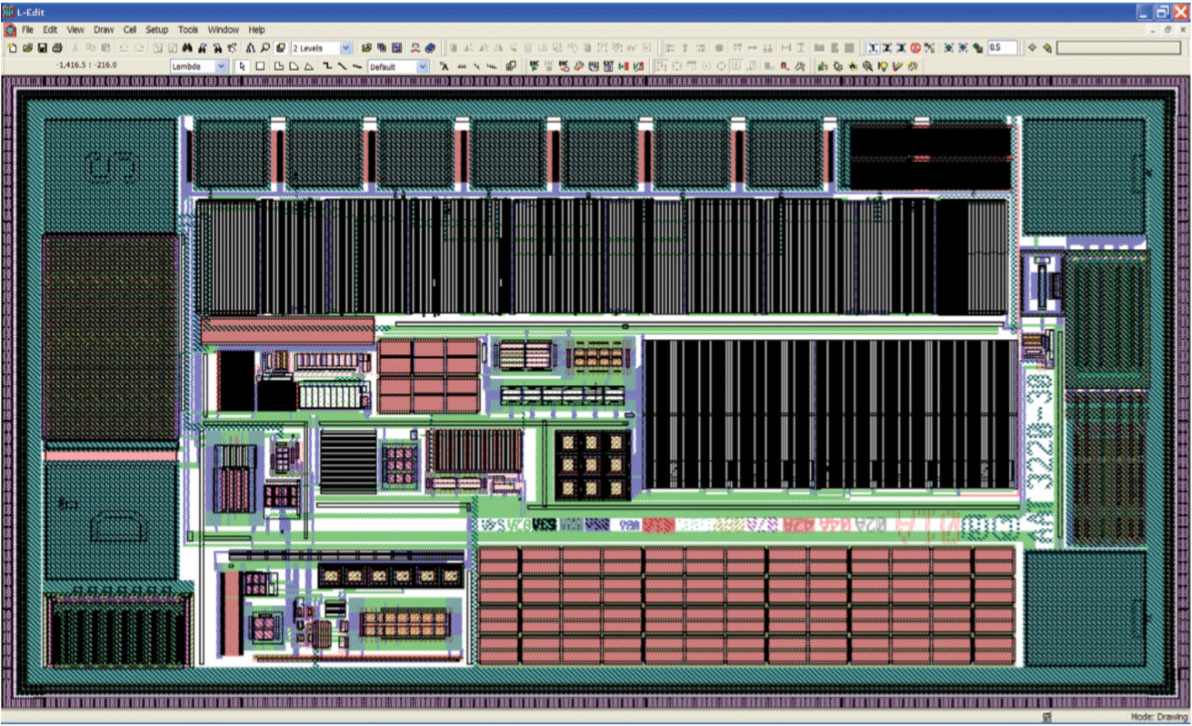

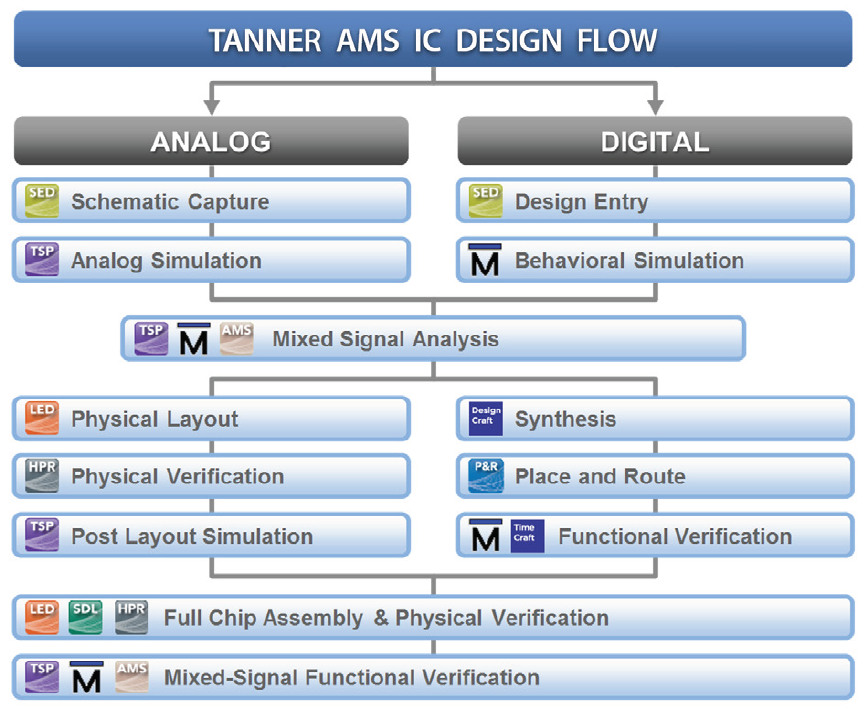

全新的Tanner ASIC套包支持完整的模拟/数模混合集成电路(IC)的设计、仿真与验证流程,包括芯片前端电路设计、Spice/VHDL/Verilog/混合信号仿真、芯片版图设计及面向Foundry工艺规则的版图验证等功能。Tanner ASIC套包以Tanner原有的版图设计工具L-Edit为核心,集成了业界普遍应用的经典工具如ModelSim、Calibre One、Eldo、EZWave等,是Mentor Graphics在模拟/数模混合芯片设计领域重点发展的、高性价比的解决方案!其中大部分环境支持Windows系统,操作界面友好,尤其适合模拟/混合芯片设计公司、物联网(IoT)行业、高校等用户学习和使用。

此外,Mentor Graphics还与主流的Foundry厂合作,定制大量的PDK并取得Foundry厂的认证,从而帮助芯片设计公司降低风险,加快产品的流片及推向市场的速度。

Tanner ASIC的关键特性:

- 支持模拟/数模混合芯片的全定制流程,易学易用

- 兼容OpenAccess、LEF/EDF、Libery和SDF等格式

- 支持不同层次模型的联合仿真,如行为级模型、RTL Block、门级和晶体管Block等

- 支持不同类型HDL语言的联合仿真和调试,如SystemVerilog、Verilog、Verilog-AMS、Verilog-A和VHDL

- 支持Top-Down层次结构及混合信号的协同仿真

- 支持高速时序分析

- 在FPGA综合过程中支持DFT参数设置

- 提供主流Foundry厂认证的PDK

- 高效率的芯片版图布局布线功能,支持任意角度布线与交互式在线DRC布线

- 自带Calibre环境,提供芯片版图验证功能,支持层次设计的DRC检查与网表提取

- 兼容Windows和Linux系统,设计数据兼容不同系统